Livt

A hardware development platform that brings expressive semantics, built-in testing, package management, and AI-ready tooling to FPGA and ASIC design — with a fast, modern workflow from the start.

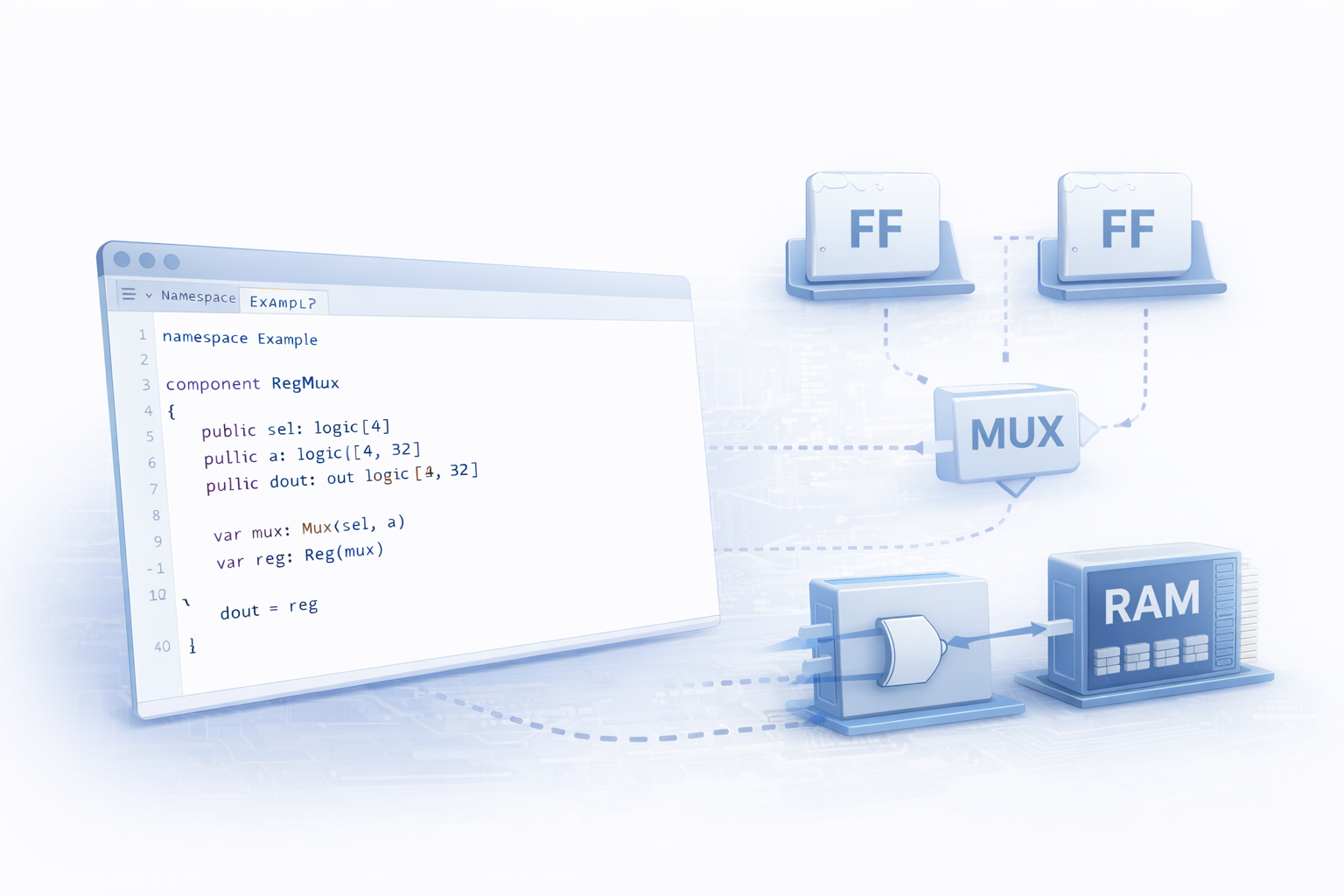

A platform whose execution model matches how FPGAs work.

Many languages that target FPGAs today were designed for CPUs — with a sequential, stack-based model — and then adapted to hardware synthesis. That mismatch leads to hidden inefficiencies, restricted language subsets, and results that are hard to predict or inspect. Livt takes a different approach: its execution model was built around hardware concurrency and dataflow from the start, so there is no mismatch to paper over.

- The language model reflects hardware concurrency rather than imposing a CPU execution model.

- Concise syntax reduces the gap between design intent and code without sacrificing precision.

- The compiler applies domain expertise to generate functionally correct VHDL.

- Common HDL pitfalls are caught at compile time rather than in simulation.

- Generated VHDL is human-readable and integrates with existing toolchains.

Test your hardware logic the way software engineers test code.

Livt has a built-in test framework so verification is a natural part of the development workflow — not a separate effort requiring manual testbench authoring. Every component can have tests, and the simulator runs them with a single command.

For hardware engineers

- Write test components alongside design components in the same project.

- No manual VHDL testbench boilerplate required.

- Simulation output is readable and clearly reports pass or failure.

- The write–build–test loop gives rapid feedback during development.

For software engineers new to FPGAs

- Familiar test patterns — annotate a component with

@Testand write test functions. - Run all tests with

livt test, just like a unit test framework. - Simulation results appear in the terminal with timestamps and messages.

component LoopbackUartTest

{

uart: LoopbackUart

new()

{

uart = new LoopbackUart()

}

@Test

fn TestLoopbackPattern()

{

uart.Transmit(0xAA)

Simulation.Wait(LoopbackUart.TICKS_PER_BIT * 12)

assert uart.IsDataAvailable() == 0b1

var received = uart.Receive()

assert received == 0xAA

}

}- 1 Verification code stays close to the hardware logic it tests.

- 2 Setup stays explicit, with the loopback instance created in the constructor.

- 3 The test drives a real UART bit pattern into the loopback path.

- 4 Assertions make the expected receive behavior easy to verify.

Processor-to-FPGA interaction built into the language.

HxS — Eccelerators' register interface generator — is integrated directly into Livt. That means defining the register interface between a processor and your FPGA design, generating the HDL, and generating the software access layer are all part of the same Livt workflow. There is no separate tool invocation, no format mismatch, and no manual synchronization between the hardware and software sides.

What this means in practice

- Define CPU-visible registers, blocks, and bus-level interface details directly from your Livt project.

- Generate VHDL register interfaces and software access code from the same interface description.

- Hardware and software teams work from a single source of truth rather than maintaining separate, diverging specs.

- Supported bus types include AXI4-Lite, Avalon, and Wishbone.

- Software access layers are generated for C/C++, Python 3, and Rust.

using Livt.IO

using Livt.HxS

@Interface(BusType="AXI4Lite")

component Controller

{

uart: Uart

new(rx: in logic, tx: out logic)

{

uart = new Uart(rx, tx)

}

@Register(Id="StatusRegister")

@Data

fn SendStatusReport()

{

uart.Send("System ready".Encode())

}

}- 1 The Livt.HxS import brings the HxS annotations into scope.

- 2 The @Interface annotation sets AXI4Lite as the bus type.

- 3 @Register and @Data define a writable register element that lets the processor trigger SendStatusReport().

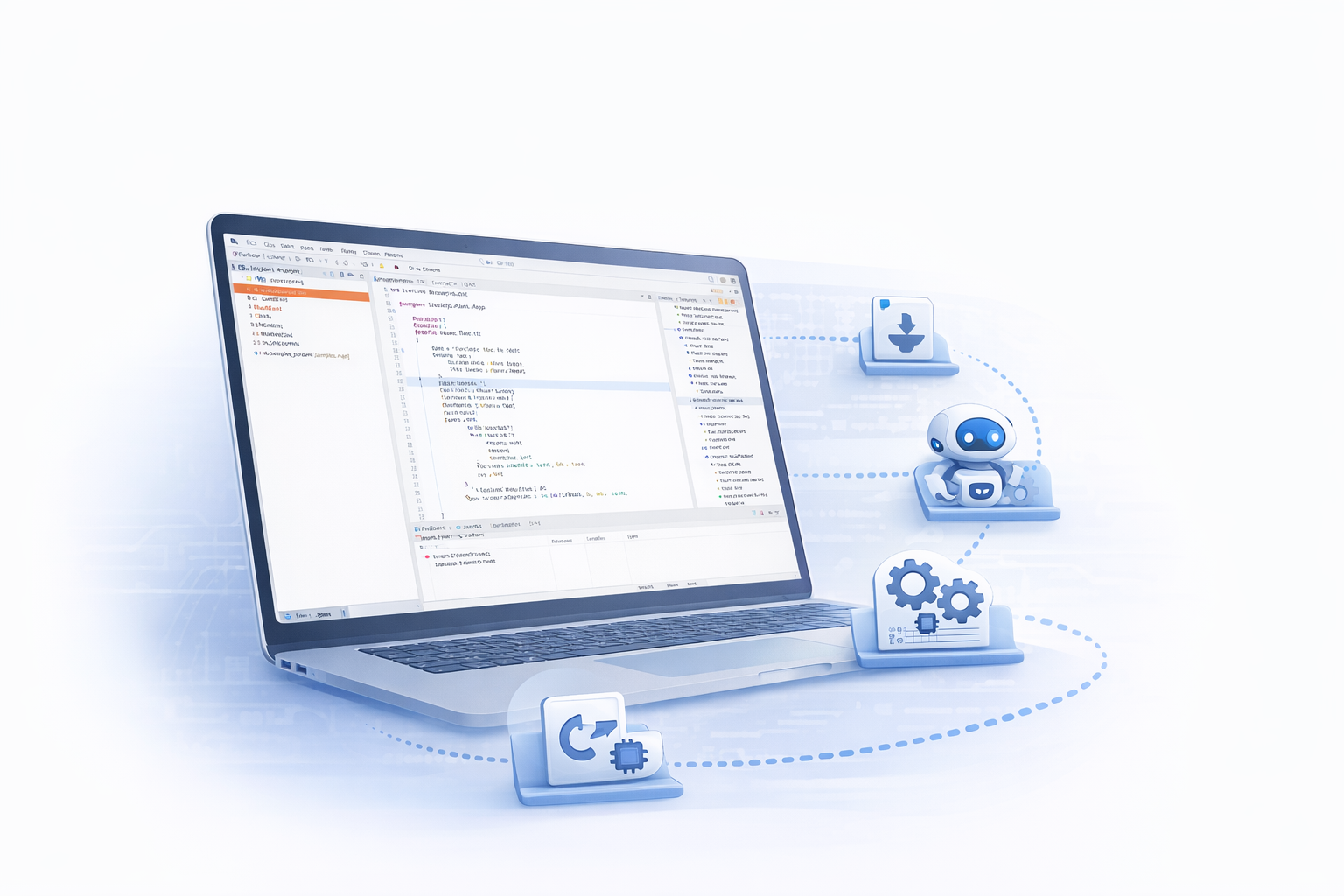

A growing ecosystem built for modern engineering workflows.

Livt is more than a language — it is the foundation for a toolchain that brings FPGA and ASIC development in line with modern software practices. Built-in package management, IDE integrations, and CI/CD support are part of the plan from the start.

- Structured, semantically rich source language — a better substrate for LLM-assisted development than raw HDL.

- Package management is provided out of the box, as a core part of the toolchain.

- A comprehensive base library with ready-to-use components and utilities.

- Frameworks for signal processing, communication protocols, and hardware-software interfaces.

Common questions about Livt

What is Livt?

Livt is a higher-level programming language and platform for FPGA and ASIC development. It is designed to bring modern software engineering ideas such as abstraction, interfaces, testing, package management, and better tooling into hardware design.

Is Livt trying to replace VHDL or Verilog?

Not in the simplistic sense. Livt is better understood as a modern frontend for hardware design. In the beginning, Livt uses VHDL as a compiler backend, but the frontend is not tied to one specific target. The higher-level semantics can be mapped to different backends through extensions.

What problem does Livt solve that HDL does not?

Traditional HDL is precise and powerful, but it exposes many low-level details directly in the source code. That makes large projects harder to maintain and evolve. Livt focuses on behavior, structure, and contracts first, so that developers can describe intent more directly and let the compiler map that intent to HDL.

How is Livt different from HLS?

HLS is very useful for turning algorithmic or compute-heavy code into hardware, especially for datapaths and accelerators. But HLS is usually centered on translating software-shaped code into RTL. Livt is different: it is intended to support modern hardware design more broadly, including architecture, interfaces, maintainability, testing, packaging, and integration.

HLS asks how software can become hardware.

Livt asks how modern hardware should be designed.

What is the role of interfaces in Livt?

Interfaces are a first-class language construct in Livt. They let developers define explicit contracts independently of any concrete implementation. This helps isolate vendor-specific details, enables testing with mocks, and makes designs easier to evolve and port.

In many FPGA projects, vendor IP is encapsulated but not truly abstracted. Livt introduces a cleaner separation between contract and implementation so that designs become more maintainable.

Is Livt only a language?

No. The broader vision is a Livt platform. That includes the language itself, package management, IDE integration, vendor integration, testing support, CI/CD concepts, and future AI-assisted tooling.

How does Livt relate to AI and LLMs?

Livt can complement AI very well. A higher-level language with stronger structure, explicit contracts, and modern tooling gives LLMs a better environment to assist developers. Rather than competing with AI, Livt can provide a more effective substrate for AI-assisted hardware development.

In an AI-assisted workflow, developers can review designs at a higher level — in terms of behavior, structure, and interfaces — rather than validating large amounts of low-level HDL. That makes review faster, clearer, and more trustworthy, while HDL generation remains the responsibility of the compiler.

Who is Livt for?

Livt is for FPGA and ASIC developers who want higher abstraction without losing hardware intent, and for software engineers who occasionally work with programmable logic and prefer a more modern development model.

Can Livt be used together with existing HDL or HLS?

Yes. Livt is designed to coexist with existing hardware design flows. Handwritten HDL modules can be integrated alongside Livt components, and HLS-generated blocks can also be used when they produce synthesizable RTL or HDL with a clear interface. In that sense, Livt can act as the architectural layer that unifies heterogeneous implementation sources.